### **DATA SHEET**

# SV4E-I3C

I3C Test and Debug Module

## **E SERIES**

## **Table of Contents**

| Introduction                                               | 3   |

|------------------------------------------------------------|-----|

| Overview                                                   |     |

| Key Benefits                                               | 3   |

| Typical Application Ordering Information                   | ∠   |

| Feature Overview                                           | 6   |

| Typical I3C Output Waveforms  Detailed Analysis Capability |     |

| Physical Connections                                       | . 8 |

| I3C Port Signal Connections                                |     |

| I3C GPIO Connections                                       | .11 |

| Specifications                                             |     |

## Introduction

#### **OVERVIEW**

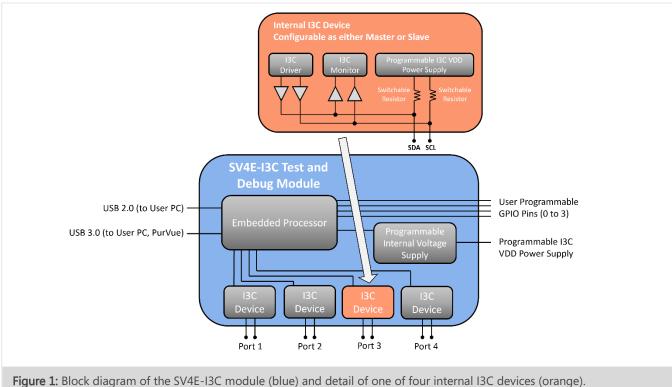

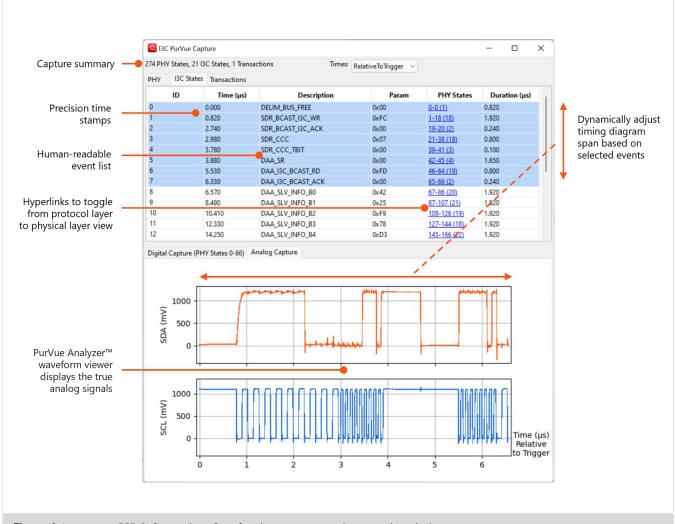

The SV4E-I3C is an all-inclusive solution for I3C-based device interface development, test, and programming. Containing three instruments in one, this tool can act as a protocol exerciser, a protocol analyzer, and a general purpose I3C device programmer. As an exerciser, it may be used to implement, test and debug both I3C controller and I3C target devices. As a protocol analyzer, it provides timing analysis with 10 ns capture resolution. The optional PurVue Analyzer™ provides a fully-embedded real-time oscilloscope (500 MHz, 12 bit) to the suite of Introspect I3C analysis tools and eliminates the need for external oscilloscope probes. As an I3C device programmer, the deep memory of the SV4E-I3C can support a wide range of device programming requirements. All three categories of instrumentation features are accessible simultaneously and in real-time using award-winning Introspect ESP Software.

## **KEY FEATURES**

- Device instances: integrates 4 parallel devices, each with its own independent protocol stack

- **Device roles:** able to configure multiple devices with different roles (main controller, secondary controller, target) with concurrent operation.

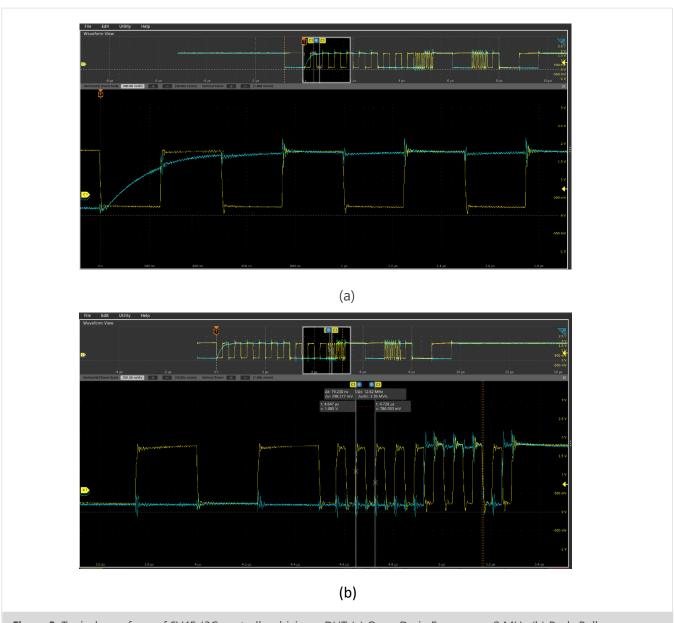

- Analog waveform analysis: fully integrated real time (500 MHz / 12 bit) oscilloscope on two simultaneous channels (SCL and SDA).

- **Protocol analysis:** easily trigger all analysis functions on CCC's and patterns for private and broadcast communications including IBI and hot-join functions.

#### **KEY BENEFITS**

- **Self-Contained:** simultaneous protocol exercising and protocol analysis enables complete characterization, debug, and test environment for individual sensor/controller devices and for entire multi-device systems

- Flexible: solution features I3C and I3C Basic protocol support with real-time voltage and timing controls

- Automated: scripting capability ideal for debug tasks, verification and full-fledged production screening of devices and system boards

## **BLOCK DIAGRAM**

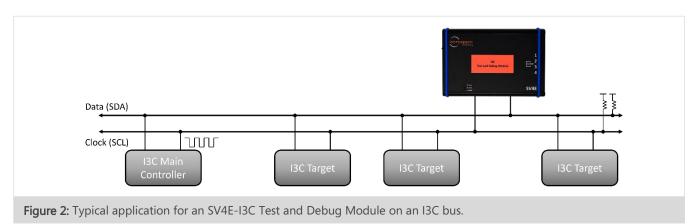

### TYPICAL APPLICATION

SV4E-I3C Test and Debug Module INTROSPECT.CA

## **ORDERING INFORMATION**

## TABLE 1: ITEM NUMBERS FOR THE SV4E-I3C

| PART NUMBER | NAME                                                       | KEY DIFFERENTIATORS                                                                                                                                                   |

|-------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6604        | SV4E-I3C Test and Debug Module<br>Standard 2.0 V Interface | Characterization, debug and test of I3C devices for I3C VDD = 0.8 to 2.0 V. Includes PC software license (perpetual) and the standard 2.0 V interface adapter board   |

| 6606        | PurVue Analyzer™ Integrated<br>Oscilloscope Option         | Option to provide PurVue Analyzer™ Protocol-Triggered Real-Time Oscilloscope to SV4E-I3C Test and Debug Module waveform capture capabilities                          |

| 6608        | SV4E-I3C with PurVue Analyzer™                             |                                                                                                                                                                       |

| 4845        | Low Voltage Adapter for SV4E-I3C                           | Standard adapter board to support 2.0 V operation                                                                                                                     |

| 4865        | High Voltage Adapter for SV4E-I3C                          | Adapter board to support 3.6 V operation                                                                                                                              |

| 5410        | I3C Target Device CTS Application                          | Based on the following CTS specifications: mipi_I3C-v1-1-1_CTS_v1-0 and I3C-Basic-v1-1-1_CTS_v1-0 Contact Introspect for Method of Implementation (MOI) documentation |

| 5418        | I3C Controller Device CTS<br>Application                   | Based on the following CTS specifications: mipi_I3C-v1-1-1_CTS_v1-0 and I3C-Basic-v1-1-1_CTS_v1-0 Contact Introspect for Method of Implementation (MOI) documentation |

## **Feature Overview**

## **TYPICAL I3C OUTPUT WAVEFORMS**

Figure 3: Typical waveform of SV4E-I3C controller driving a DUT (a) Open Drain Frequency=2 MHz (b) Push-Pull Frequency=12.5 MHz

#### **DETAILED ANALYSIS CAPABILITY**

Figure 4: Introspect ESP Software interface for data capture and protocol analysis

## **Physical Connections**

Figure 5 shows the physical connections on the SV4E-I3C module. The four I3C Ports (SCL and SDA) are available via 0.1" female header connections. A programmable power supply for VDD of the I3C bus and four programmable general purpose I/Os are each available via separate 0.1" male header connectors. Please see the following section for a detailed description of each of the header pinouts.

The SV4E-I3C has a USB port that allows the SV4E to communicate directly with a PC through USB cable connections on the left side of the module. Power is provided to the SV4E-I3C module with a 12 V DC supply through a barrel connector. The recommended DC power supply, included with the SV4E-I3C module, is produced by CUI Incorporated, Part # CUI SDI65-12-U-P5.

Figure 5: (a) Physical connections to the SV4E-I3C module (b) close-up view of the SV4E-I3C interface board

#### **NOTE**

The SV4E-I3C is available with two interface options: the standard 2.0 V interface and an extended 3.6 V interface (refer to the ordering information in Table 1). The hardware differences between the two options are contained within the interface board connected to the right side of the SV4E-I3C module, as shown above. The two options require separate firmware versions.

### **13C PORT SIGNAL CONNECTIONS**

The SV4E-I3C module has a 16 pin female header providing connections to all four I3C ports. The connector is from Samtec (part number BCS-108-L-D-TE) and the pinout for the connector is provided in Table 2 below.

TABLE 2: SV4E I3C SIGNAL PINS

| I3C PORT<br>CONNECTOR DIAGRAM           | PIN<br>NUMBER                | SIGNAL<br>NAME | SIGNAL DESCRIPTION |

|-----------------------------------------|------------------------------|----------------|--------------------|

| Pin 16 Pin 15                           | 2                            | SCL1           | Port 1 I3C Clock   |

| PIN 16 PIN 15                           | 4                            | SDA1           | Port 1 I3C Data    |

|                                         | 6                            | SCL2           | Port 2 I3C Clock   |

| 1 2                                     | 8                            | SDA2           | Port 2 I3C Data    |

| 3 4 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 | 10                           | SCL3           | Port 3 I3C Clock   |

| SV4E                                    | 12                           | SDA3           | Port 3 I3C Data    |

| Pin 2 Pin 1                             | 14                           | SCL4           | Port 4 I3C Clock   |

|                                         | 16                           | SDA4           | Port 4 I3C Data    |

|                                         | 1, 3, 5, 7, 9,<br>11, 13, 15 | Ground         | Ground             |

Introspect also provides eight standard 6" jumper cables for rapid connection between the connector and the device under test. Jumper cables are compatible with the female header part number provided above.

### **I3C PROGRAMMABLE POWER SUPPLY**

The SV4E-I3C module has a 2 pin header providing a direct connection to the VDD supply for the I3C bus. The bus voltage is set directly in Introspect ESP software.

The connector is a standard 0.100" male header (Mill Max Manufacturing, part number 350-10-102-00-006000) and the pinout for the connector is provided in Table 3. If this power supply is brought directly to a DUT board, please ensure that appropriate power supply decoupling is applied where connections are made.

The programmable range of this supply varies according to the interface option used (refer to Table 1). For the standard 2.0 V product, the VDD supply voltage range is 1.0 V to 2.02 V. For the extended range 3.6 V product, the VDD supply voltage range is 2.0 V to 3.6 V. The VDD supply supports up to 1.0 A of output currents across the full output voltage range. Also refer to Table 6 in the specifications section of the document.

TABLE 3: SV4E PROGRAMMABLE POWER SUPPLIES

| PROGRAMMABLE POWER SUPPLY, J3 CONNECTOR DIAGRAM | PIN<br>NUMBER | SIGNAL<br>NAME       | SIGNAL DESCRIPTION                                                                                                                                                                                              |

|-------------------------------------------------|---------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                 | 1             | Ground               | Ground                                                                                                                                                                                                          |

| Pin 2 SV4E Pin 1                                | 2             | I3C VDD<br>(I3C Bus) | User programmable power supply for VDD for I3C bus. This supply is also used for the logic "1" voltage level for GPIO_2 and GPIO_3 for the standard 2.0 V interface (refer to the next section and to Table 4). |

#### **13C GPIO CONNECTIONS**

The SV4E-I3C module has an 8-pin header providing connections to four GPIO pins. The connector is a standard 0.100" male header (Sullins, part number PREC004DAAN-RC) and the pinout for the connector is provided in Table 4.

GPIO\_0 and GPIO\_1 operate with 1.8 V LVCMOS logic and voltage characteristics which are provided in Table 10 in the "Specifications" section of the document.

GPIO\_2 and GPIO\_3 voltage characteristics vary according to the interface option used (refer to Table 1). For the standard 2.0 V product, the GPIO\_2 and GPIO\_3 logic "1" voltage levels track the programmable VDD for I3C bus (refer to Table 3). For the extended range 3.6 V product, the GPIO\_2 and GPIO\_3 pins operate with 1.8 V LVCMOS logic described in Table 10 in the "Specifications" section of this document.

TABLE 4: SV4E GPIO PINS

| GPIO, J2<br>CONNECTOR DIAGRAM | PIN<br>NUMBER | SIGNAL<br>NAME      | SIGNAL DESCRIPTION                                                                                                                              |

|-------------------------------|---------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|                               | 1, 2          | Reserved            | Reserved                                                                                                                                        |

|                               | 3             | RESET_N<br>(GPIO_0) | SV4E reset pin, active low  ("0" = reset, "1" = not in reset)  Logic "1" voltage = 1.8 V  Logic "0" voltage = 0 V                               |

| Pin 1                         | 4             | GPIO_1              | User configurable, input or output<br>Logic "1" voltage = 1.8 V<br>Logic "0" voltage = 0 V                                                      |

| Pin 7 Pin 1 Pin 2             | 5             | GPIO_2              | User configurable, input or output<br>Logic "1" voltage = I3C VDD or 1.8 V<br>(see the description above this table)<br>Logic "0" voltage = 0 V |

|                               | 6             | GPIO_3              | User configurable, input or output<br>Logic "1" voltage = I3C VDD or 1.8 V<br>(see the description above this table)<br>Logic "0" voltage = 0 V |

|                               | 7, 8          | Ground              | Ground                                                                                                                                          |

## Additional Documentation

SV4E-I3C Quick Start Manual

• EN-G035E-E-20100 - SV4E-I3C Quick Start Manual

SV4E-I3C PurVue Analyzer<sup>TM</sup> Product Brief

• EN-D034E-E-22154 - I3C PurVue Analyzer™ Product Brief

# Specifications

TABLE 5: GENERAL SPECIFICATIONS

| PARAMETER                                                | VALUE     | UNITS | DESCRIPTION AND CONDITIONS                                                     |

|----------------------------------------------------------|-----------|-------|--------------------------------------------------------------------------------|

| Protocol                                                 |           |       |                                                                                |

|                                                          | MIPI I3C  |       | MIPI I3C version 1.0 and 1.1<br>MIPI I3C Basic                                 |

|                                                          |           |       | JESD82-511 DDR5 RCD<br>JESD403B Sideband Bus                                   |

| Physical Layer Interface                                 | JEDEC 13C |       | JESD300-5 SPD<br>JESD301-1A PMIC<br>JESD301-2 PMIC                             |

|                                                          |           |       | JESD301-2 PMIC JESD302-1 TS5110 Thermal Sensor JESD302-1 TS5111 Thermal Sensor |

| I3C Controller Device Support                            | Yes       |       | Includes I2C support                                                           |

| I3C Target Device Support                                | Yes       |       | Includes I2C support                                                           |

| Ports                                                    |           |       |                                                                                |

| Number of I3C device instances                           | 4         |       | Each fully configurable as controller, secondary controller, or target.        |

| Number of GPIO pins                                      | 4         |       |                                                                                |

| Programmable On-Board Power Supplies                     | 1         |       |                                                                                |

| Connections to PC for<br>Introspect ESP Software Control | 2         |       | USB 2.0<br>USB 3.0 (for I3C PurVue Analyzer™)                                  |

| Memory                                                   |           |       |                                                                                |

| On-board memory                                          | 1         | GByte |                                                                                |

| Power Consumption                                        |           |       |                                                                                |

| DC Input Voltage                                         | 12        | V     | DC Input Voltage                                                               |

| Maximum Current Draw                                     | 1.6       | А     | Typical operating current draw                                                 |

TABLE 6: I3C BUS SPECIFICATIONS

| PARAMETER                      | VALUE | UNITS | DESCRIPTION AND CONDITIONS            |

|--------------------------------|-------|-------|---------------------------------------|

| Physical Line Characteristics  |       |       |                                       |

| Internal SCL and SDA pull-up:  |       |       | In open drain mode, a 500 Ohm pull-   |

| Push-Pull                      | N/A   |       | up resistance to I3C VDD is           |

| Open Drain Mode                | 500   | Ohm   | automatically switched onto the line  |

| High Keeper                    | 10    | kOhm  | when required                         |

| Pin Capacitance                | 2.5   | рF    | Typical                               |

| Programmed operating voltage   |       |       |                                       |

| Standard 2.0 V Interface:      |       |       |                                       |

| Minimum Programmed VDD voltage | 800   | mV    | VDD sets SCL and SDA high voltage     |

| Maximum Programmed VDD voltage | 2020  | mV    |                                       |

| Extended 3.6 V Interface:      |       |       |                                       |

| Minimum Programmed VDD voltage | 2000  | mV    | VDD sets SCL and SDA high voltage     |

| Maximum Programmed VDD voltage | 3600  | mV    |                                       |

| VDD resolution                 | 1     | mV    |                                       |

| Operating Frequencies          |       |       |                                       |

| Minimum Open Drain Frequency   | 0.25  | MHz   |                                       |

| Maximum Open Drain Frequency   | 5.0   | MHz   |                                       |

| Minimum Push-Pull Frequency    | 0.25  | MHz   |                                       |

| Maximum Push-Pull Frequency    | 12.5  | MHz   |                                       |

| Minimum Legacy I2C Frequency   | 0.002 | MHz   | Interoperates with legacy I2C devices |

| Maximum Legacy I2C Frequency   | 1     | MHz   | Interoperates with legacy I2C devices |

TABLE 7: I3C BUS TIMING SPECIFICATIONS

| PARAMETER                            | VALUE | UNITS | DESCRIPTION AND CONDITIONS                                                                                                                                         |

|--------------------------------------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCL / SDA Timing                     |       |       |                                                                                                                                                                    |

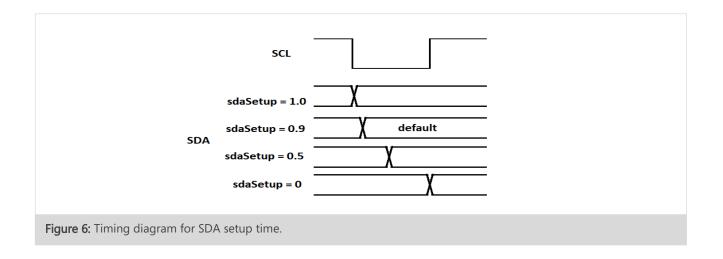

| SDA Setup Time Range                 | 1.0   | UI    | Specification for the timing from SCL falling edge to the following SDA edge, expressed as a fraction of the UI. See Figure 6 on following page.                   |

| Independent SDA Setup Timing         | Yes   |       | SDA setup time is set independently<br>for I3C Open Drain, I3C Push Pull, and<br>I2C operation                                                                     |

| SCL to SDA Skew Injection Resolution | 2.5 * | ns    | Timing resolution, SCL to SDA for 12.5 MHz Push-Pull Operation. Please see footnote below. A diagram of SDA setup time is shown in Figure 6 on the following page. |

| Duty Cycle Timing Resolution         | 10    | ns    |                                                                                                                                                                    |

| Protocol Analyzer Timing Resolution  | 10    | ns    | Timing resolution for the digital protocol analyzer. The PurVue Analyzer has greater timing resolution, refer to Table 8.                                          |

<sup>\*</sup> This 2.5 ns timing resolution may be selectively applied to any one of the parameters listed below. All other timing parameters may be set with 10 ns resolution.

Push-Pull SDA setup time

HDR / DDR Positive SDA setup time

HDR / DDR Negative SDA setup time

Start or Repeated Start hold time (t<sub>CAS</sub> or t<sub>CASr</sub>)

Repeated Start setup time (t<sub>CBSr</sub>)

Stop setup time  $(t_{CBP})$

TABLE 8: PURVUE ANALYZER™ SPECIFICATIONS

| PARAMETER                   | VALUE | UNITS | DESCRIPTION AND CONDITIONS             |

|-----------------------------|-------|-------|----------------------------------------|

| General Performance         |       |       |                                        |

| Number of Channels          | 2     |       | Analysis for SCL and SDA of one port   |

| Minimum Input Voltage       | -500  | mV    |                                        |

| Maximum Input Voltage       | 3600  | mV    |                                        |

| Oscilloscope Resolution     | 12    | bit   | 1 mV resolution at full input range    |

| Ossillassana Triagarina     |       |       | Oscilloscope captures are triggered by |

| Oscilloscope Triggering     |       |       | I3C protocol events                    |

| Sampling Rate               | 1.0   | GHz   | Maximum sampling rate                  |

| Data Transfer (via USB 3.0) | 5.0   | Gbps  | Provides rapid waveform uploads        |

TABLE 9: I3C MODES AND OPERATIONS

| PARAMETER                           | VALUE            | UNITS | DESCRIPTION AND CONDITIONS          |

|-------------------------------------|------------------|-------|-------------------------------------|

| Additional supported features       |                  |       |                                     |

|                                     | CCC<br>Direct RW |       |                                     |

| Operations                          | Private RW       |       |                                     |

|                                     | Hot-Join         |       |                                     |

|                                     | IBI              |       |                                     |

| Signaling Modes                     | SDR              |       |                                     |

| Signaling Wodes                     | HDR-DDR          |       |                                     |

| Mixed Bus Mode Support              | Yes              |       |                                     |

| 50 ns Spike Filter                  | Yes              |       | Automatic for mixed bus mode        |

|                                     |                  |       | ACK/NACK behavior                   |

| Error Injection                     | Yes              |       | Flipped parity bit                  |

|                                     |                  |       | Setup time and hold time violations |

| Protocol Analysis                   | Yes              |       |                                     |

| Offline Capability / Tri-State Mode | Yes              |       | Tri-state mode for SCL/SDA pins     |

TABLE 10: 1.8 V LVCMOS GPIO CHARACTERISTICS

| PARAMETER               | VALUE | UNITS | DESCRIPTION AND CONDITIONS             |

|-------------------------|-------|-------|----------------------------------------|

| Voltage                 |       |       |                                        |

| Voltage Level           | 1.8   | V     | All values on the left are listed for  |

| V <sub>IL</sub> minimum | -0.3  | V     | 1.8 V LVCMOS logic only. See page 11   |

| V <sub>IL</sub> maximum | 0.7   | V     | and Table 4 for a list of all possible |

| V <sub>IH</sub> minimum | 1.5   | V     | voltage levels supported by the GPIO   |

| V <sub>IH</sub> maximum | 2.25  | V     | pins.                                  |

| V <sub>OL</sub> maximum | 0.4   | V     |                                        |

| V <sub>OH</sub> minimum | 1.7   | V     |                                        |

| REVISION NUMBER | HISTORY                                                           | DATE               |

|-----------------|-------------------------------------------------------------------|--------------------|

| 1.0             | Document Release                                                  | June 8, 2020       |

| 1.1             | Updated specifications                                            | April 24, 2021     |

| 1.2             | Updated specifications, description of new features               | June 3, 2022       |

| 1.3             | Updated specifications, improved pinout clarity in Figures 2 to 4 | September 20, 2022 |

The information in this document is subject to change without notice and should not be construed as a commitment by Introspect Technology. While reasonable precautions have been taken, Introspect Technology assumes no responsibility for any errors that may appear in this document.