# DATA SHEET

# SV5C-eDP

Embedded DisplayPort Generator

# **C** SERIES

© Introspect Technology, 2023 Published in Canada on November 20, 2023 EN-D026E-E-23324

INTROSPECT.CA

TABLE OF CONTENTS

# Table of Contents

| 3 |

|---|

| 3 |

| 3 |

| 4 |

| 6 |

| 5 |

| ( |

# Introduction

## **OVERVIEW**

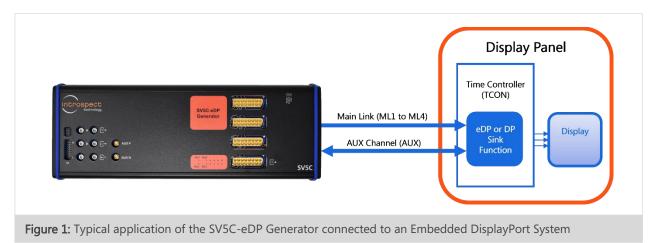

The **SV5C-eDP Embedded DisplayPort Generator** is an ultra-portable, high-performance instrument capable of generating traffic for Embedded DisplayPort and DisplayPort applications at data rates of up to 12.5 Gbps. The SV5C-eDP Generator provides analog parameter controls that enable DisplayPort receiver stress-testing and allow for deep insights into voltage and timing sensitivities of DisplayPort sink devices. The instrument operates with Introspect Technology's award-winning software, Pinetree, which includes full pattern synthesis tools for generating test patterns and video frames for system-level test. Figure 1 below illustrates a typical application of the SV5C-eDP Generator in an Embedded DisplayPort system.

## **KEY FEATURES**

- Protocol: supports Embedded DisplayPort up to v1.5 and DisplayPort up to v2.1 in HBR

- Supported Data Rates: up to 12.5 Gbps with a fully continuous range of data rates

- Lane Count: configurable from 1 to 4 lanes per port plus Auxiliary Channel

- Analog Controls: voltage amplitude and common mode voltage, each per lane

- Signal Impairments: jitter injection, sinusoidal voltage noise injection, per-wire timing skew

- Pattern Generation: full video frame generation with 2 GBytes of pattern memory

#### **PHYSICAL CONNECTIONS**

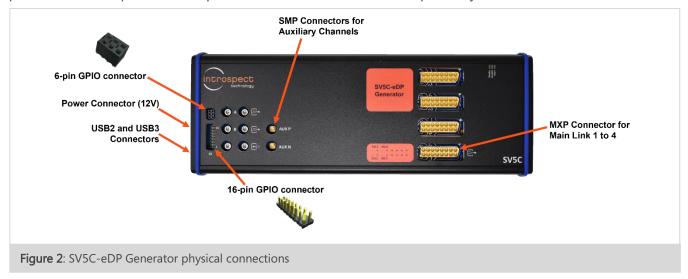

The physical connections of the SV5C-eDP Generator are shown in Figure 2. The lanes (main link 1 to 4) are contained on a single MXP connector, as shown in the figure. The pin mapping for the Main Link, 6-pin GPIO and 16-pin GPIO are provided in Tables 1, 2, and 3, respectively.

#### TABLE 1: MAIN LINK MXP CONNECTOR PINOUT

| CONNECTOR    | PIN | LANE         |

|--------------|-----|--------------|

|              | 12  | Main Link 1P |

| 1 16         | 11  | Main Link 1N |

| 2 15         | 10  | Main Link 2P |

| 3 14 4 13    | 9   | Main Link 2N |

| 5 12         | 7   | Main Link 3P |

| 6 11<br>7 10 | 8   | Main Link 3N |

| 8 9          | 5   | Main Link 4P |

|              | 6   | Main Link 4N |

SV5C-eDP Embedded DisplayPort Generator

#### TABLE 2: 6-PIN GPIO CONNECTOR PINOUT

| CONNECTOR                                                                                                                                                                                 | PIN | SIGNAL NAME | PIN | SIGNAL NAME |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|-----|-------------|

| 6-pin GPIO connector                                                                                                                                                                      | 1   | Ground      | 2   | 3V          |

| Samtec BCS-103-F-D-TE                                                                                                                                                                     | 3   | Ground      | 4   | 1.8V        |

| $Pin 1 \longrightarrow \bigcirc \bigcirc$ | 5   | Ground      | 6   | 1.2V        |

#### TABLE 3: 16-PIN GPIO CONNECTOR PINOUT

| CONNECTOR                                                                                                                                                                     | PIN         | FUNCTION                                          | PIN | FUNCTION                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------------------------------|-----|----------------------------|

| 16-pin GPIO connector                                                                                                                                                         | 1           | HPD 1.2V Out                                      | 2   | User IO 1                  |

| Samtec MTLW-108-05-G-<br>D-200                                                                                                                                                | 3           | HPD 3.3V Out / HPD<br>From Programmable<br>DAC In | 4   | User IO 2                  |

| Pin 16 $\longrightarrow$ $\bigcirc$                                                                                                                                           | 5           | Ground                                            | 6   | User IO 3                  |

|                                                                                                                                                                               | 7           | Reserved                                          | 8   | User IO 4                  |

|                                                                                                                                                                               | 9           | Ground                                            | 10  | User IO 5                  |

| $\bigcirc \bigcirc $ | 11          | Reserved                                          | 12  | User I2C SCL Controller    |

|                                                                                                                                                                               | 13 Reserved | Reserved                                          | 14  | User I2C SDA Controller    |

| All User IO pins use<br>1.8V LVCMOS logic and<br>have a weak internal pull-<br>up.                                                                                            | 15          | Reserved                                          | 16  | HPD 1.8V Out / HPD 1.8V In |

|                                                                                                                                                                               |             |                                                   |     |                            |

SV5C-eDP Embedded DisplayPort Generator

## **ORDERING INFORMATION**

TABLE 4: ITEM NUMBERS FOR THE SV5C-EDP GENERATOR WITH RELATED PRODUCTS

| PART NUMBER | NAME                                                 | KEY DIFFERENTIATORS                                             |

|-------------|------------------------------------------------------|-----------------------------------------------------------------|

| 5740        | SV5C-eDP Analyzer (includes<br>Pinetree SW license)  | High performance eDP protocol<br>analyzer and eDP source tester |

| 5741        | SV5C-eDP Generator (includes<br>Pinetree SW license) | High performance eDP protocol generator and eDP sink tester     |

# Specifications

## TABLE 5: GENERAL SPECIFICATIONS

| PARAMETER                                   | VALUE     | UNITS | DSECRIPTION AND<br>CONDITIONS                                                   |

|---------------------------------------------|-----------|-------|---------------------------------------------------------------------------------|

| Application / Protocol                      |           |       |                                                                                 |

| Physical Layer Interface                    | eDP<br>DP |       | Support for eDP up to version 1.5<br>Support for DP up to version 2.1 in<br>HBR |

| Ports                                       |           |       |                                                                                 |

| Number of Transmitter Lanes                 | 5         |       | Main Link 1, 2, 3, 4<br>Auxiliary Channel (bidirectional)                       |

| Number of GPIO pins                         | 5         |       | Programmable as external trigger input or flag output pins                      |

| Number of dedicated reference clock inputs  | 1         |       |                                                                                 |

| Number of dedicated reference clock outputs | 2         |       |                                                                                 |

| PC connections for Pinetree<br>Control      | 2         |       | USB2 and USB3                                                                   |

SV5C-eDP Embedded DisplayPort Generator

| Data Rates and Reference Clocks |        |      |          |

|---------------------------------|--------|------|----------|

| Minimum Data Rate               | 1562.6 | Mbps | Per Lane |

| Maximum Data Rate               | 12.5   | Gbps | Per Lane |

| Minimum External Input Clock    | 10     | MHz  |          |

| Maximum External Input Clock    | 250    | MHz  |          |

| Minimum External Output Clock   | 10     | MHz  |          |

| Maximum External Output Clock   | 500    | MHz  |          |

| Power Consumption               |        |      |          |

| DC Input Voltage                | 12     | V    |          |

| Power Dissipation               | 100    | W    |          |

#### TABLE 6: EDP TRANSMITTER LANE CHARACTERISTICS

| PARAMETER                      | VALUE     | UNITS | DESCRIPTION AND<br>CONDITIONS       |

|--------------------------------|-----------|-------|-------------------------------------|

| HS Voltage Performance         |           |       |                                     |

| Minimum Output Voltage Swing   | 20        | mV    | Differential                        |

| Maximum Output Voltage Swing   | 850       | mV    | Differential                        |

| Voltage Swing Resolution       | 10        | mV    | Differential                        |

| Voltage Swing Accuracy         | 10% or 10 | mV    | The larger value of 10% or 10 mV    |

| Minimum Common Mode Voltage    | -20       | mV    |                                     |

| Maximum Common Mode Voltage    | 750       | mV    |                                     |

| Common Mode Voltage Resolution | 1         | mV    |                                     |

| Common Mode Voltage Accuracy   | 20% or 20 | mV    | The larger value of 20% or 20 mV    |

| Swing and Common Mode Setting  | Per Lane  |       |                                     |

| HS Timing Performance          |           |       |                                     |

| Rise and Fall Time             | 30        | ps    | Typical, fastest slew rate setting  |

|                                |           |       | 20% to 80%                          |

| Slew Rate Range                | 13        | V/ns  | Difference between the fastest slew |

|                                |           |       | rate and the slowest slew rate      |

| De-Emphasis Performance          |          |     |                                         |

|----------------------------------|----------|-----|-----------------------------------------|

| Pre-Tap 1 Range                  | +/- 150  | mV  | FIR taps defined as additive increments |

| Pre-Tap 1 Resolution             | 10       | mV  |                                         |

| Post-Tap 1 Range                 | +/- 300  | mV  |                                         |

| Post-Tap 1 Resolution            | 10       | mV  |                                         |

| Post-Tap 2 Range                 | +/- 150  | mV  |                                         |

| Post-Tap 2 Resolution            | 10       | mV  |                                         |

| De-Emphasis Setting              | Per Lane |     |                                         |

| Transmitter Lane Output Coupling |          |     |                                         |

| Output Differential Impedance    | 100      | Ohm |                                         |

| Differential Impedance Tolerance | +/- 10   | Ohm |                                         |

#### TABLE 7: EDP TRANSMITTER SIGNAL IMPAIRMENT CHARACTERISTICS

| PARAMETER                                     | VALUE     | UNITS  | DESCRIPTION AND<br>CONDITIONS    |

|-----------------------------------------------|-----------|--------|----------------------------------|

| Noise Floor                                   |           |        |                                  |

| Random Jitter (RMS)                           | < 1.2     | ps rms |                                  |

| Deterministic Jitter Injection                |           |        |                                  |

| Minimum Sinusoidal Frequency                  | 0.1       | kHz    | Per lane                         |

| Maximum Sinusoidal Frequency                  | 50        | MHz    | Per lane                         |

| Frequency Resolution                          | 0.1       | kHz    |                                  |

| Maximum Sinusoidal Amplitude                  | 16000     | ps     | Peak-Peak, tested to 1000 ps     |

| Sinusoidal Amplitude Resolution               | 500       | fs     |                                  |

| Sinusoidal Amplitude Accuracy                 | 10% or 10 | ps     | The larger value of 10% or 10 ps |

| Voltage Noise Injection                       |           |        |                                  |

| Maximum Amplitude of Common<br>Mode Noise     | 40        | mV     |                                  |

| Maximum Amplitude of Difference<br>Mode Noise | 80        | mV     |                                  |

SV5C-eDP Embedded DisplayPort Generator

| Amplitude Resolution of Injected<br>Noise | 1       | mV  |                                     |

|-------------------------------------------|---------|-----|-------------------------------------|

| Maximum Frequency of Injected<br>Noise    | 1       | GHz |                                     |

| Channel Skew Performance                  |         |     |                                     |

| Coarse Skew Range:                        |         |     | Lane to lane                        |

| Programmable Skew                         | +/- 20  | UI  | Hardware is capable of larger skews |

| Coarse Skew Resolution:                   |         |     | Lane to lane                        |

| 1.62 Gbps, 2.7 Gbps                       | 0.25    | UI  |                                     |

| 5.4 Gbps                                  | 0.5     | UI  |                                     |

| 8.1 Gbps                                  | 1       | UI  |                                     |

| Fine Skew Range:                          |         |     | Wire to wire and lane to lane       |

| Programmable Skew                         | +/- 500 | ps  | Hardware is capable of larger skews |

#### TABLE 8: PATTERN HANDLING CHARACTERISTICS

| PARAMETER                                          | VALUE | UNITS  | DESCRIPTION AND<br>CONDITIONS                                                                                |

|----------------------------------------------------|-------|--------|--------------------------------------------------------------------------------------------------------------|

| User-Programmable Pattern Memory                   |       |        |                                                                                                              |

| Minimum Pattern Segment Size                       | 8     | Bits   |                                                                                                              |

| Maximum Pattern Segment Size                       | 2     | GBytes |                                                                                                              |

| Total Memory Space for Transmitters                | 2     | GBytes |                                                                                                              |

| Pattern Sequencer                                  |       |        |                                                                                                              |

| Sequence Control                                   | Yes   |        | Loop infinite<br>Loop-on-count (see count below)<br>Play to end                                              |

| Number of Sequencer Slots per<br>Pattern Generator | 16    |        | Each pattern generator can string up<br>to 16 different segments together,<br>each with its own repeat count |

| Number of Entry Slots                              | 1     |        | Separate from above 16 segments                                                                              |

| Number of Exit Slots                               | 1     |        | Separate from above 16 segments                                                                              |

| Maximum Repeat Count Per Slot                      | 65536 |        |                                                                                                              |

| Maximum Repeat Count for Outer<br>Loop             | 65536 |        | Outer loop can encompass any number of slots                                                                 |

| Additional Pattern Characteristics                 |       |        |                                                                                                              |

| Pattern Switching                                  | Yes   |        | Wait to end of segment, or immediate                                                                         |

#### TABLE 9: DISPLAYPORT FEATURES

| PARAMETER                                | VALUE                | DESCRIPTION AND CONDITIONS                                                                                                                                                                                                       |

|------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Features                                 |                      |                                                                                                                                                                                                                                  |

| Framing Modes                            | Standard<br>Enhanced |                                                                                                                                                                                                                                  |

| Supported Pixel Formats                  | RAW<br>RGB<br>YCbCr  | RAW6, RAW8, RAW9, RAW10, RAW11,<br>RAW12, RAW14, RAW16<br>RGB666, RGB888, RGB999, RGB101010,<br>RGB111111, RGB121212, RGB161616<br>YCbCr422, YCbCr444 and Y-Only at:<br>6 bit, 8 bit, 9 bit, 10 bit, 11 bit,<br>12 bit and 16bit |

| Supported YCbCr Standard                 | YCbCr601<br>YCbCr709 |                                                                                                                                                                                                                                  |

| Display Stream Compression (DSC)         | 1.1, 1.2             |                                                                                                                                                                                                                                  |

| Data Scrambling                          | Yes                  | DP Seed, eDP Seed                                                                                                                                                                                                                |

| Forward Error Correction (FEC)           | Yes                  |                                                                                                                                                                                                                                  |

| Advanced Link Power Management<br>(ALPM) | AUX-wake<br>AUX-less |                                                                                                                                                                                                                                  |

| Adaptive-Sync (AS)                       |                      |                                                                                                                                                                                                                                  |

| Panel Self Refresh 1 & 2 (PSR)           | Yes                  |                                                                                                                                                                                                                                  |

| Panel Replay (PR)                        |                      |                                                                                                                                                                                                                                  |

| Audio                                    | Yes                  |                                                                                                                                                                                                                                  |

| Hot Plug Detect (HPD)                    | Yes                  | Standard<br>Low voltage HPD                                                                                                                                                                                                      |

#### TABLE 10: PHYSICAL CHARACTERISTICS

| PARAMETER                | VALUE     | UNITS  | DESCRIPTION AND<br>CONDITIONS |  |

|--------------------------|-----------|--------|-------------------------------|--|

| Dimensions               |           |        |                               |  |

| Length                   | 11, 280   | in, mm |                               |  |

| Width                    | 4.25, 108 | in, mm |                               |  |

| Height                   | 1.7, 43   | in, mm |                               |  |

| Weight                   | 2.5       | lbs    |                               |  |

| Physical Connections     |           |        |                               |  |

| ML4 to ML1, Aux Channel  | MXP       |        | Huber & Suhner, 16 pin        |  |

| 6-pin GPIO               |           |        | Samtec BCS-103-F-D-TE         |  |

| 16-pin GPIO              |           |        | Samtec MTLW-108-05-G-D-200    |  |

| Ref Clock In             | SMP       |        | SMP Differential Pair         |  |

| Ref Clock Out            | SMP       |        | SMP Differential Pair         |  |

| PC connection            | USB2      |        | USB2.0 mini B                 |  |

|                          | USB3      |        | USB3.0 micro B                |  |

| Power Switch / Connector |           |        | AC adapter provided           |  |

|                          |           |        | 110/220 V, 50/60 Hz           |  |

| REVISION NUMBER | HISTORY                                                                                                                      | DATE              |

|-----------------|------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 1.0             | Document Release                                                                                                             | December 16, 2021 |

| 1.1             | Updated the maximum output voltage swing specification                                                                       | May 20, 2022      |

| 1.2             | Updated the Molex Pinout and DP<br>& eDP supported versions                                                                  | May 24, 2023      |

| 1.3             | Updated images of the SV5C-eDP<br>Generator; physical connections &<br>connector pin-out; DisplayPort<br>Features in Table 9 | November 20, 2023 |

The information in this document is subject to change without notice and should not be construed as a commitment by Introspect Technology. While reasonable precautions have been taken, Introspect Technology assumes no responsibility for any errors that may appear in this document.

© Introspect Technology, 2023 Published in Canada on November 20, 2023 EN-D026E-E-23324

INTROSPECT.CA